# Layout-Based 3D Solid Modeling of IC Structures and Interconnects Including Electrical Parameter Extraction

Xiaoning Qi, Sherry Y. Shen, Ze-Kai Hsiau, Zhiping Yu, and Robert Dutton

Center for Integrated Systems, Stanford University CISX 335, Stanford University Stanford, CA 94305-4075, USA

# Outline

- Background and Motivation

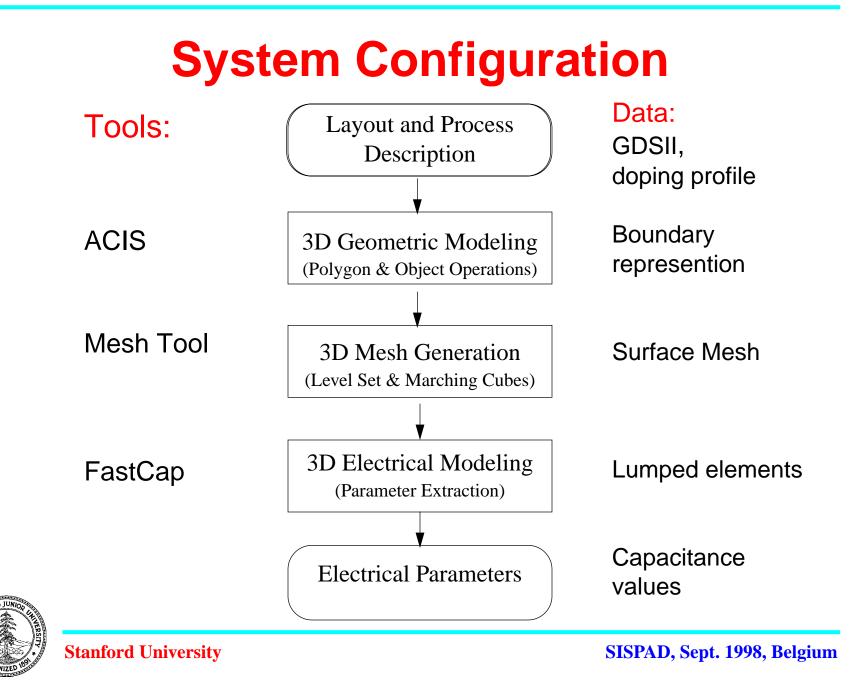

- System Configuration

- Layout-Based 3D Solid Modeling

- Level-Set Method for Surface Meshing of Complex Geometry

- Capacitance Extraction for a Four-Transistor SRAM Cell

- Summary and Discussion

#### **Background and Motivation**

**Stanford University**

#### **Background and Motivation**

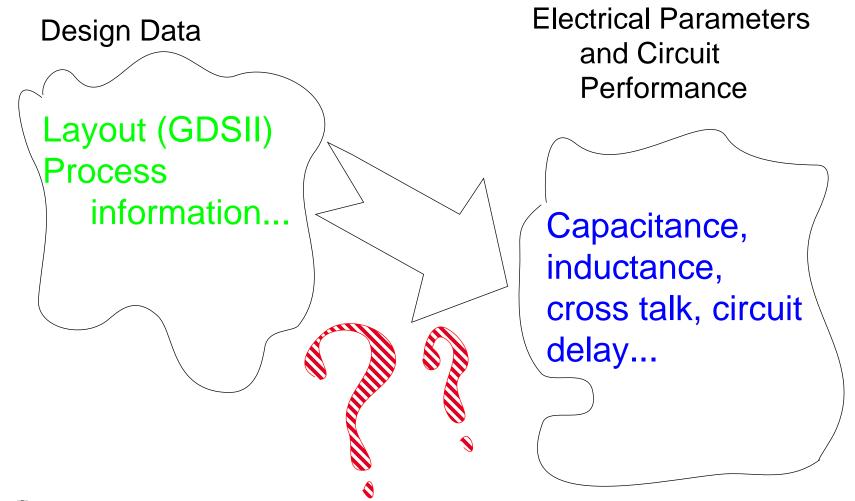

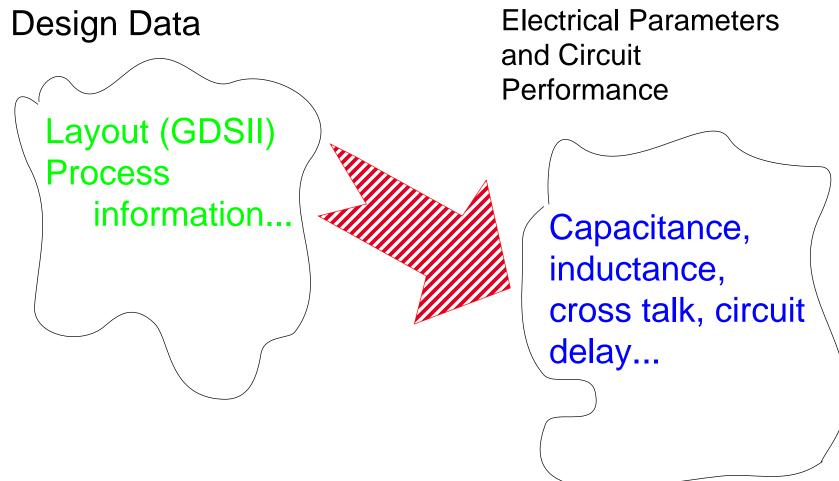

- Timely technology development requires the prediction of circuit performance based directly on the design data.

- Need to link directly the impact of layout and processing on the electrical characteristics of complex IC structures and interconnects.

- Current commercial tools are still evolving to provide abilities of modeling IC structures with complex 3D geometry.

#### **System Configuration**

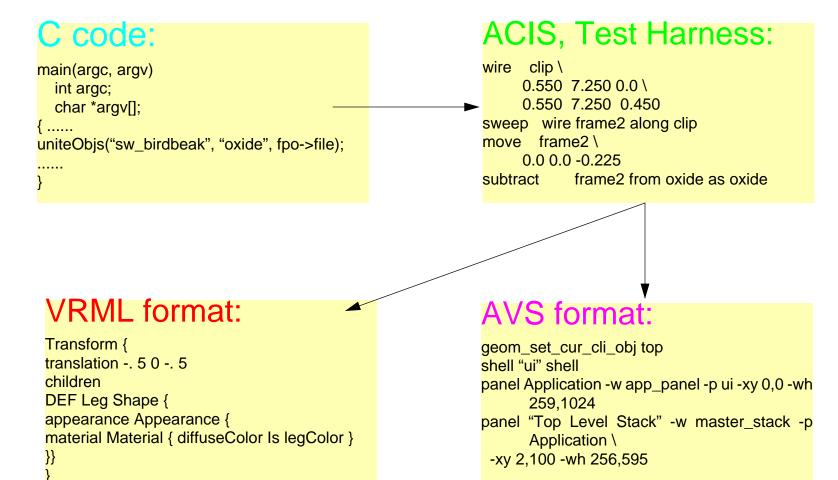

- Generating input files for the geometry modeler to specify the structure of each component in a 3D object

- Running the geometry modeler to obtain description files for the geometry

- Converting the output files from the geometry modeler to geometry files readable to 3D visualization program

- Displaying and manipulating 3D image using the visualization program

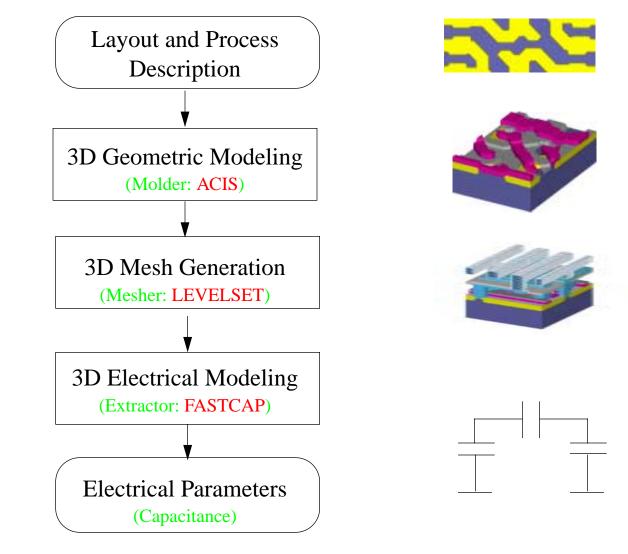

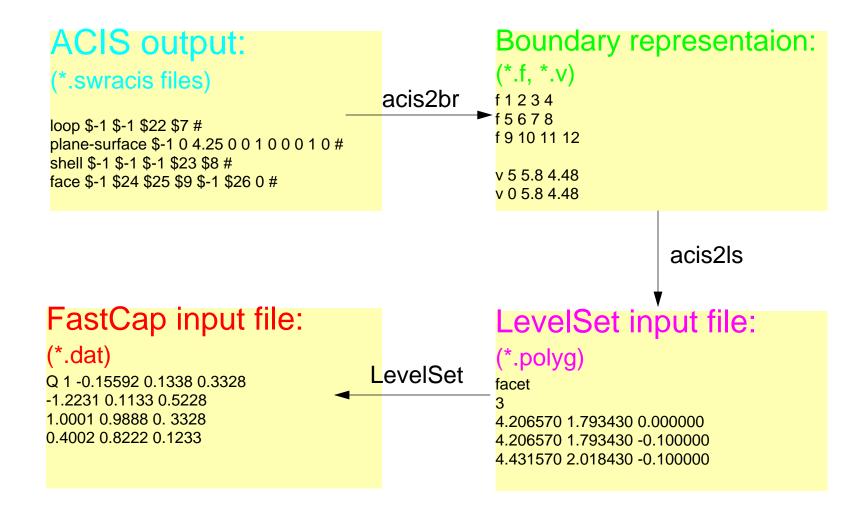

#### **Solid Modeling to Elec. Extraction**

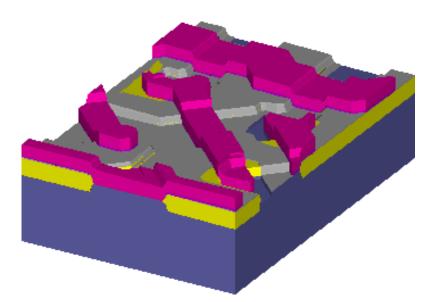

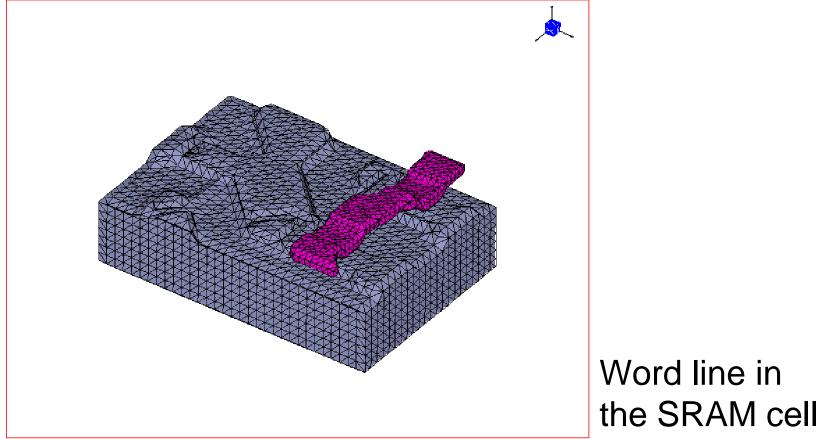

# Solid geometry after the first poly layer is formed.

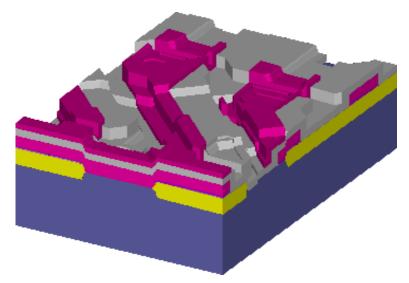

# Solid geometry after the second poly layer is formed.

**Stanford University**

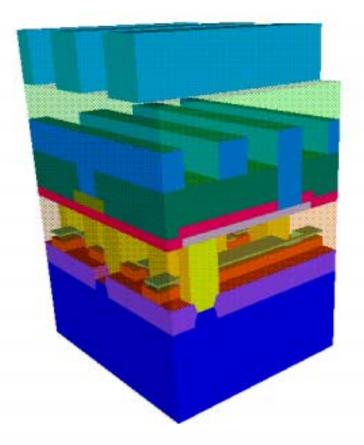

- SRAM in VRML format displayed by VRML browser across Internet with two insulating layers transparent

# Level-Set Method for Surface Meshing of Complex Geometry

- Surface polygons from the solid modeler are triangulated into a coarse mesh.

- Octants containing the geometric object are subdivided recursively until a predefined refinement criteria is satisfied.

- Octants intersecting the surface are segmented into triangles.

- Local connectivity is extracted from the octree grid.

# Level-Set Method for Surface Meshing of Complex Geometry

**Stanford University**

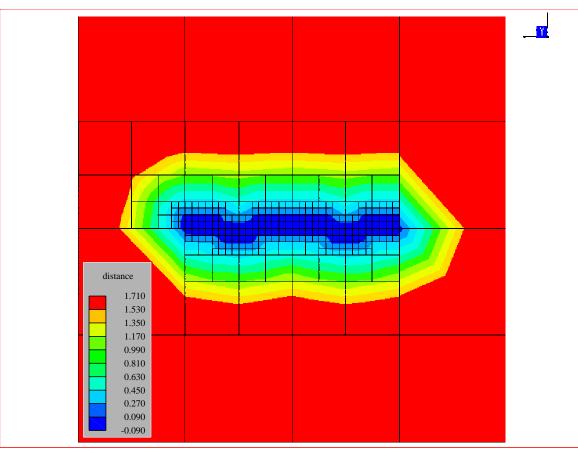

#### Level-Set Method for Surface Meshing (cont'd)

Mesh sectioning and distance contour for the word line

**Stanford University**

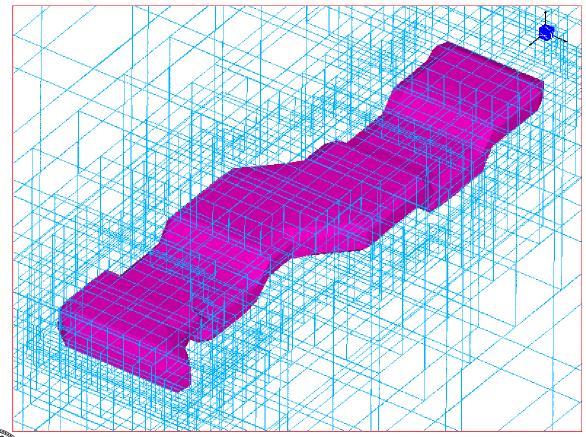

# Level-Set Method for Surface Meshing (cont'd)

Iso-surface and octree for the word line

**Stanford University**

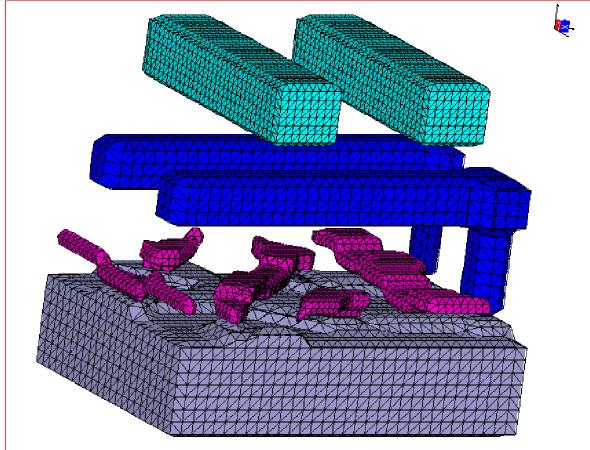

# Level-Set Method for Surface Meshing (cont'd)

Mesh result for substrate, first poly layer and metal layers

#### **Capacitance Extraction**

- FASTCAP is used to analyze the realistic structures.

- The complete electrical model that FASTCAP provides for the word line vs. substrate:

#### **Capacitance Extraction**

Capacitance among word line, bit lines and substrate:

|           | substrate | word line | bit line1 | bit line2 |

|-----------|-----------|-----------|-----------|-----------|

| substrate | 2.92      | 1.27      | 0.36      | 0.36      |

| word line |           | 1.57      | 0.12      | 0.13      |

| bit line1 |           |           | 1.01      | 0.27      |

| bit line2 |           |           |           | 1.02      |

Table 1: Capacitance Extraction Results (fF)

#### **Realized Link from Geom. to Elec.**

# Conclusions

- A technology based interconnect modeling approach

- More realistic 3D geometry modeling which can be updated based on the design of layout and process specification

- More robust and efficient level-set meshing capabilities

- More accurate electrical parameter extraction based on realistic structures.

# **Related Work**

- To model packaging parasitics (e.g. bonding wire's inductance) based on fast 3D geometry capturing (to be presented in IEDM '98, S.F.)

- To combine 3D solid modeling of package/ bonding-wire with compact model of RF power devices (BJT, LDMOS) to provide macro model for circuit simulation (SPICE, MDS)

- On-chip interconnect analysis including inductance and EMI.