This project addresses modeling and simulation of noise in advanced silicon-based devices, with special emphasis on hetero-junction transistors. The increased frequency performance of both HFET and HBT transistors fabricated in silicon hold great promise for high-frequency RF applications. However, the noise properties and how they scale with device dimensions are of paramount importance. This project, jointly with collaborators in Germany (Profs. Meinerzagen and Jungemann) exploits both Monte Carlo (MC) and Hydro-Dynamic (HD) device simulators to characterize noise properties in advanced Silicon-Germanium hetero-junction transistors as well as in conventional CMOS. Several CIS Partner companies are supporting and collaborating in this project-currently Philips, Matsushita and Infineon.

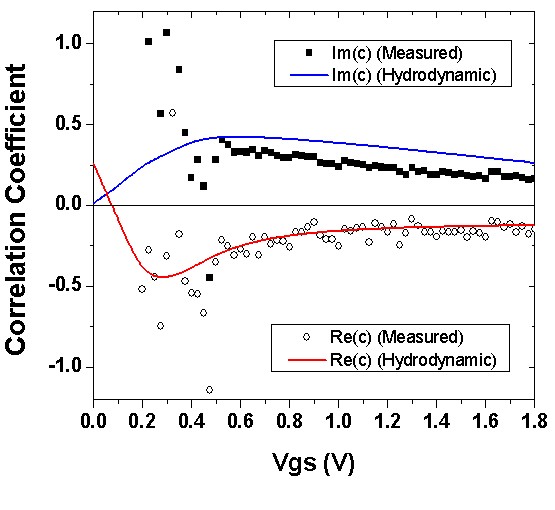

Measured Data and HD-based Device Simulations for CMOS Transistor

Contact webmaster with questions regarding this page.

Last updated August 5, 2004.

All rights reserved. ©2004 Board of Trustees of the Stanford University